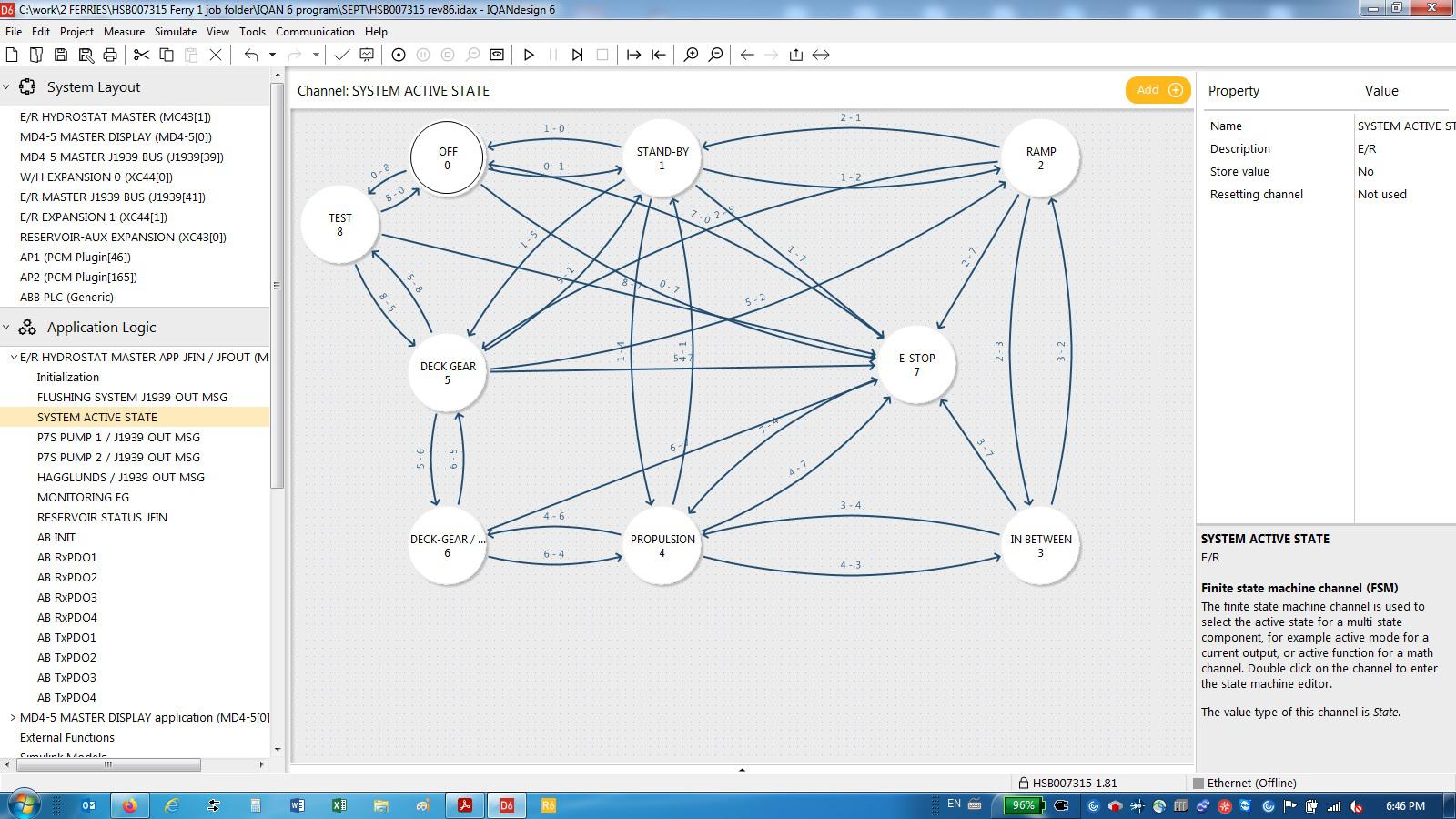

FINITE STATE BETWEEN MASTER MODULES LOCKING UP

I have a system where I have an MD4-5 connected to an MC43 in a multi-master system, using both APPIN/APPOUT and J1939 messages between them.

I have implemented a FINITE STATE MACHINE in the MD4-5 master, and send the representative code to an identical mock-up of FSM in the MC43 (with all the same links).

For some reason I have cases where the MC43 system will either revert back from one state (4) to 0 and then back again (very briefly). At other times, I can see on my screen a J1939 (or APPIN) message (since I've tried it both ways), where the input number is 6, but the FSM in the MC43 will stay at 5 and not change to 6. What is also strange is that there is no path from 4 to 0 in my FSM design (though I suspect the default value on a CAN error, even with the master bus, is 0).

I am running IQANDesign 6.02.7.5650 (and hope to get an update if our new license code arrives)

Customer support service by UserEcho

The APPIN channel has a property for Error value, default is 0 but you can change this:

This error value is used if there channel status is in error, when there is a timeout you can see the APPIN status is timeout if you measure with IQANdesign/IQANrun.