Stored Timers resetting after sending Settings

Stored Timers resetting after sending Settings

We are noticing that Timer channels (with Store Value set to "Yes") - that we use as hour counters in our machines - are being reset when sending a settings file to that machine. The values that they are being reset to, are the values of the timers from the machine that the settings file is pulled from.

The timers have respective Digital Parameters (adjust items) that are used to reset them, with a Function Parameter (adjust item) specifying the Reset Value.

However, when a settings file is sent to a machine, the timers do not reset to 0 or to the "Reset Value" but rather to the value of the timer from machine that the settings file was pulled from.

Please advise.

Module IO automatically scrolls to top of page

Module IO automatically scrolls to top of page

I'm transferring information shown on the module page (all the IO) to a 2D cad program so I can draw electrical schematics simultaneously. This involves selecting an input / output in IQAN design and also hovering over it to gather information such as pin number and DIN-AC details etc. If we have scrolled down the page to get to the selected input/output to select and I move onto the cad program on a different monitor on the PC, clicking back into IQAN design window to view the next IO, it always returns to the top.

Its a bit frustrating as I then have to find where I left off, and adds some time to the task I'm carrying out. Its mainly because I loose a visual of the input I was on.

Can it remain in the same scroll position as it was when I left the window? I'm not closing IQAN design and re-opening, its still open and visible on a separate second display.

7.04.8.10088

Generic CAN Paged message grouping

Generic CAN Paged message grouping

I have run into an issue while trying to read NMEA2000 data from 2 engines. The message uses pages to transmit data across 4 messages and has an engine instance in the first page. I cant mask for the engine instance in the last 3 pages.

It would be nice to have a multipage option like the J1939 Frame for NMEA2000 messages. If that could be combined with masking for instance value, that would solve my issue.

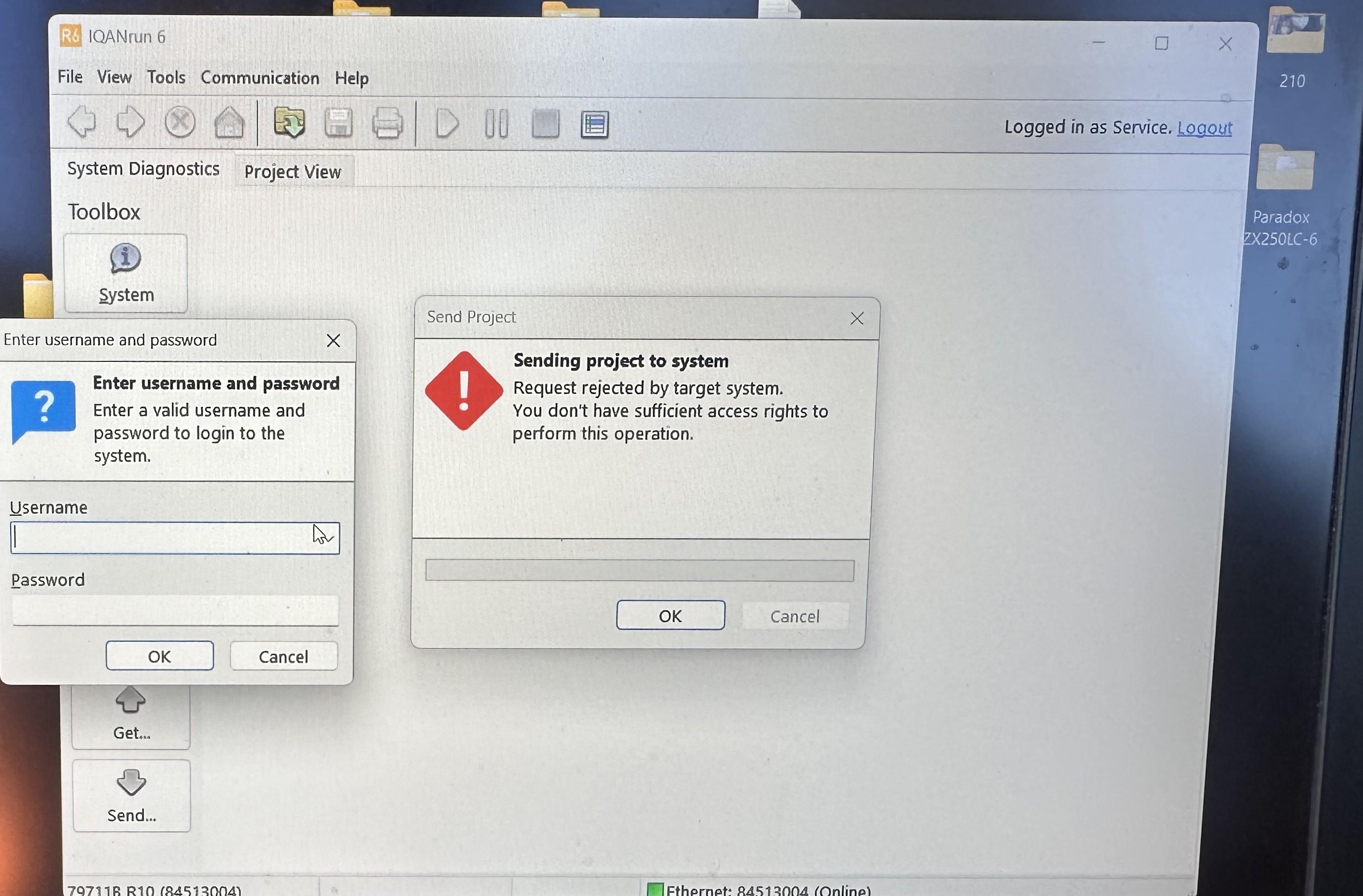

Don't have Sufficient Rights to send Project

Don't have Sufficient Rights to send Project

Has anyone come across this problem - the machine has been logged into with Service access and password and then keeps asking for the password again and always rejects when trying to update with a project file.

IqanRun 6 is being used in this case.

not possible to download latest iqan software 7

not possible to download latest iqan software 7

the downloadlink to iqan design 7 doesnt work

Can Multiple Users Connect to MC41 Simultaneously via IQANGo?

Can Multiple Users Connect to MC41 Simultaneously via IQANGo?

Hi folks,

I am wanting to use IQANgo as a system monitor application for the end users, with locked down access level.

Can anyone with experience tell me if it is possible to have multiple simultaneous users connect to an MC controller all at the same time over ethernet?

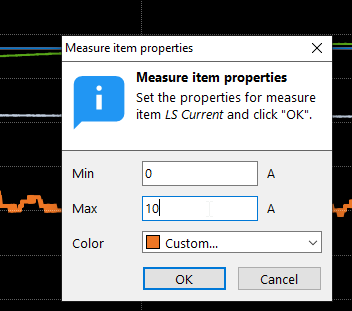

IQANRun 7 measure min / max

Hello!

Once a Measure is recorderd, in IQANRun 6 you could adjust Min / Max range in case it was not properly defined on the project, so you can still view the graph with the correct scale if necessary:

Now in IQANRun 7 I can not find such property. Can it be adjusted somewhere? How?

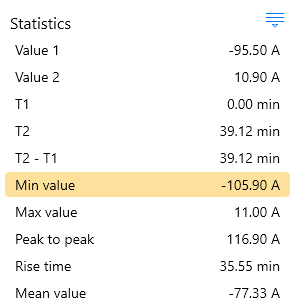

I only manage to see the statistics:

If this feature has been removed i think it's a significant step back, as it was very usefull. In such case please consider adding it back. Thanks!

Customer support service by UserEcho